Densité et nanomètres : de la technique au marketing

Préambule : dans ce petit article il ne s’agit pas de dire que l’entreprise X et meilleure que l’entreprise Y. Le but premier est de comprendre que les nanomètres sont maintenant mis en avant avec un but marketing, en oubliant de parler de la densité. Et quand le marketing s’empare de la technique, la simplification nous éloigne souvent de la vérité.

Depuis quelques années maintenant, la finesse de gravure exprimée en nanomètres, est devenue un argument qui permet de vanter l’avance technologique de certains. Les entreprises disposant de leurs propres capacités de fabrications n’ont donc de cesse de communiquer sur l’évolution de leurs processus. Samsung, TSMC et IBM sont depuis quelques temps dans une course poursuite alors qu’Intel a souvent déclenché l’ironie avec la déclinaison sans fin de son 14nm et ses dérivés « +++ ».

Pourtant, nombreux sont ceux qui ont relativisé cette course à la finesse de gravure. Pour eux, si la finesse du process est évidemment une avancée technologique, elle n’est pas l’assurance de meilleures performances. Intel a longtemps mis en avant cet argument en étant accusé de mauvaise foi. Pourtant, si on se sort du monde du CPU, on a bien pu constater qu’AMD, malgré son process 7nm, n’avait pas toutes les armes face à Nvidia. La densité et les nanomètres n’évoluant pas suivant une certaine symétrie.

Quelle est la donnée la plus pertinente ?

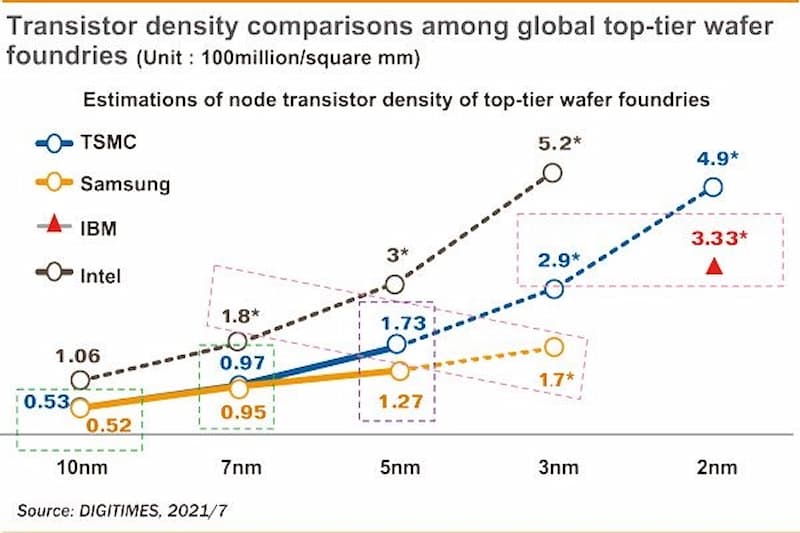

Digitimes a publié un rapport de recherche mis à jour qui analyse la densité du processus de fabrication des semi-conducteurs en provenance de chez TSMC, Intel, Samsung et IBM. L’étude se propose de comparer les processus de fabrication en 10 nm, 7 nm, 5 nm, 3 nm et 2 nm pour voir qu’elle est la différence réelle entre ces entreprises.

Et la première chose qui frappe si on suite cette étude c’est que le 10 nm SuperFin d’Intel est plus dense (106 millions de transistors par mm2) que le 7 nm de TSMC ou de Samsung. Intel pense que son futur 7nm sera aussi supérieur sur ce point au 5nm de TSMC ou à celui de Samsung.

On rentre ensuite dans la spéculation car on doit analyser non plus les faits mais les données transmises par ces entreprises. En suivant cette logique, les 5nm d’Intel seraient plus de deux fois plus denses que le même process 5nm de Samsung et presque le double par rapport à ceux de TSMC. Allons plus loin, les 5nm d’Intel sont presque aussi dense que le 2nm d’IBM (300 contre 333 millions par mm2).

Il faut bien ne pas oublier que la seule la densité est prise en compte ici. La consommation d’énergie, les coûts, etc. ne sont pas pris en compte, mais cette analyse permet de se faire une autre opinion. La finesse de gravure ne peut pas être la seule clé de compréhension pour se faire une idée sur la complexité et la technicité d’une puce, voir sa puissance.

En analysant les données suivant ce prisme, on peut constater que Samsung qui communique beaucoup sur ses évolutions de la finesse de son process, a en réalité de sérieuses difficultés à suivre TSMC et Intel.

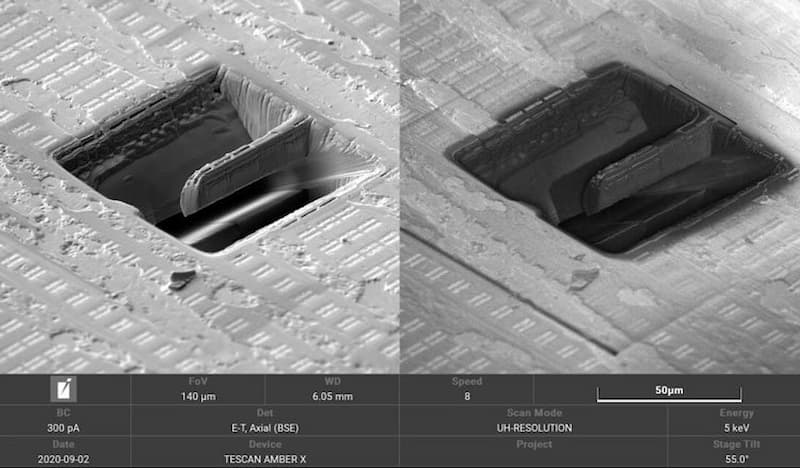

Si vous souhaitez aller plus loin, prenez le temps de regarder la vidéo de Der8auer et son utilisation du microscope électronique ( image plus haut ).

et même la densité est une valeur « flottante » car elle va dépendre de ce qui est gravé: du logique (coeur), du statique, (cache) ou de l’analogique (IO).

en exemple le CPU IBM Z15 de 13mld de T gravé en … 14nm GloFo et qui surpasse la densité du… 5nm TSMC!!! Merci le cache de 1,3Go 8o) !

en vrai au final je regarde pas la Densité et nanomètre je regarde que le resultal final amd > intel actuellement dans presque tout les situation